- 国内站

- 国际站

无数据

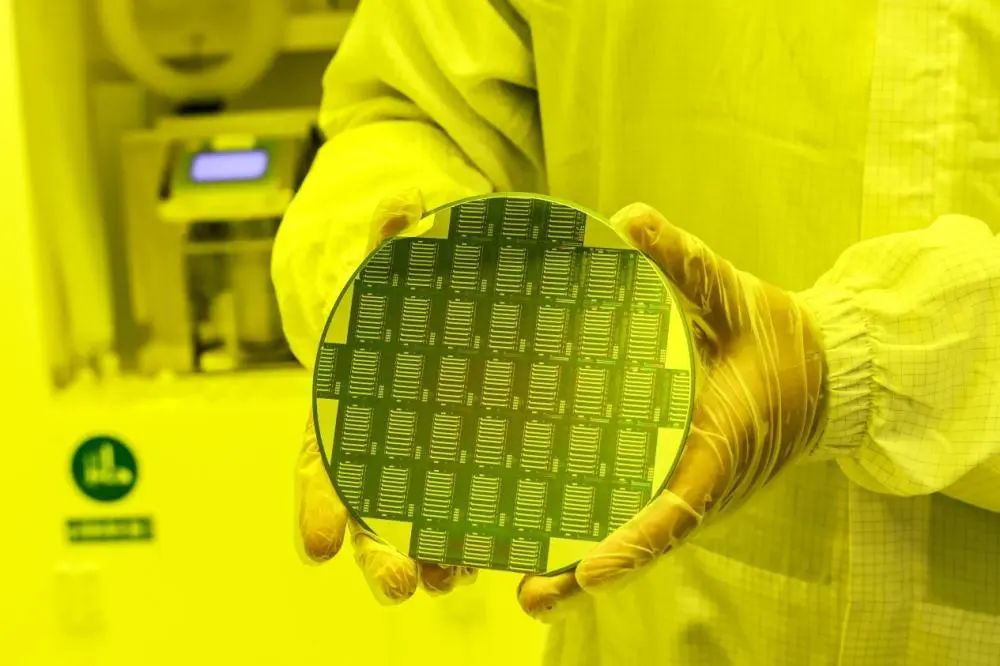

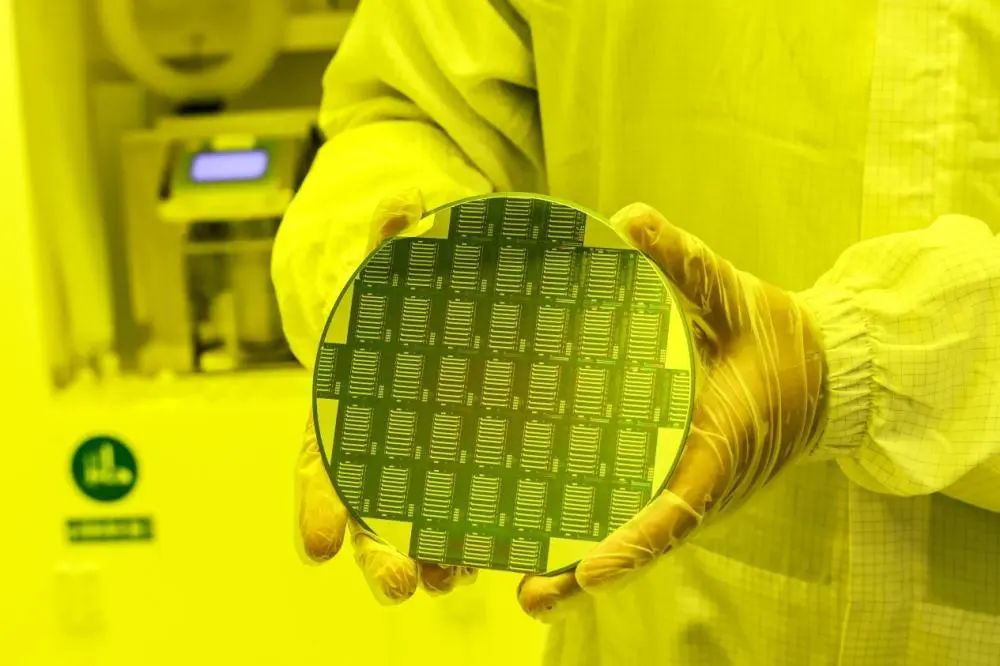

入选国家工信部「首批重点培育中试平台」名单不到1个月,上海交大无锡光子芯片研究院(CHIPX)再次迎来重磅时刻——6月5日,首片6寸薄膜铌酸锂光子芯片晶圆在国内首个光子芯片中试线下线,同时实现了超低损耗、超高带宽的高性能薄膜铌酸锂调制器芯片的规模化量产,关键技术指标达到国际先进水平。

据悉,这一突破性成果标志着我国在高端光电子核心器件领域完成从「技术跟跑」到「产业领跑」的历史性跨越。研究院将依托中试平台,携手产业链合作伙伴推进规模化量产进程,构建「技术研发-工艺验证-规模量产」全链条能力,进一步增强自主可控的量子科技国际竞争力。

自主可控中试平台,实现晶圆级光子芯片集成工艺突破

光量子芯片是光量子计算的核心硬件载体,其产业化进程将推动我国在量子信息领域实现自主可控,更是抢占全球量子科技竞争制高点的战略支撑。此前,因共性关键工艺技术平台的缺失,我国光量子技术面临「实验室成果难以量产」的困境,是制约产业发展的「卡脖子」难题,而光子芯片中试线的启用成为破局关键。

作为无锡市滨湖区竞速量子科技赛道的「头号工程」,也是区域未来产业地标,上海交大无锡光子芯片研究院于2022年底破土动工,并率先启动国内首条光子芯片中试线建设。上海交大无锡光子芯片研究院于2022年12月启动国内首条光子芯片中试线建设,2024年9月,集光子芯片研发、设计、加工和应用于一体的光子芯片中试线正式启用。如今,首片晶圆成功下线,中试平台实现量产通线,彰显了项目建设的高效与成果。

作为一种高性能光电材料,薄膜铌酸锂具备超快电光效应、高带宽、低功耗等优势,在5G通信、量子计算等领域展现出巨大潜力。然而,由于薄膜铌酸锂材料脆性大,大尺寸薄膜铌酸锂晶圆的制备一直被行业视为挑战,尤其在量产化工艺中面临纳米级加工精度控制、薄膜沉积均匀性保证、刻蚀速率一致性调控等三大难题。

CHIPX工艺团队基于自主建设的国内首条光子芯片中试线,引进了110余台国际顶级CMOS工艺设备,覆盖了薄膜铌酸锂晶圆从光刻、薄膜沉积、刻蚀、湿法、切割、量测到封装的全闭环工艺。通过创新性开发芯片设计、工艺方案与设备系统的协同适配技术,成功打通了从光刻图形化、精密刻蚀、薄膜沉积到封装测试的全制程工艺,实现晶圆级光子芯片集成工艺突破。

性能指标国内领先,高性能薄膜铌酸锂调制器芯片实现规模化量产

凭借中试平台先进的纳米级加工设备和快速工艺迭代能力,工艺团队通过大量工艺验证与优化,以深紫外(DUV)光刻与薄膜刻蚀的组合工艺,系统性地解决了晶圆级光子芯片集成的关键技术瓶颈:在6寸铌酸锂晶圆上实现了110nm高精度波导刻蚀;通过步进式(i-line)光刻完成了高均一性、纳米级波导与复杂高性能电极结构的跨尺度集成,达到顶尖制程水平。

同时,工艺团队通过材料-器件协同设计创新,在兼顾高集成度的同时,实现了性能的跨越式突破,关键指标全面领先。

工艺纳入PDK体系,中试平台赋能产业生态

中试平台,一头连着创新,一头连着产业。在不断提升自身科技创新能力的同时,研究院还打造了开放共享的服务生态,赋能产业发展。

近期,研究院将发布PDK工艺设计包,本次高性能薄膜铌酸锂调制器芯片的核心工艺参数与器件模型已全面纳入、开放共享。该版本PDK不仅集成无源耦合器、分束器、波导阵列和有源热相移器、电光调制器等基础元件模型,同时涵盖多物理场协同仿真模块,构建起标准化光子芯片设计体系。

重构智算新范式,赋能国家战略需求

除了赋能产业发展,上海交大无锡光子芯片研究院此次双重成果突破更具里程碑意义,正加速推动芯片化光子集成趋势下的产业链重构进程。

在人工智能算力需求呈指数级增长的当下,传统电子器件面临功耗高、带宽受限两大核心瓶颈。高性能薄膜铌酸锂调制器凭借超低损耗、超高带宽、超快传输速率优势,能支撑云计算、超算中心和5G/6G基础设施的场景需求;基于该技术的光计算芯片,以「光传输+光计算」的融合方案,实现高并行、低延迟、低功耗的AI推理与训练计算架构,从底层破解AI大模型训练的算力困局,正成为AI算力新基建的核心支撑。

随着技术链逐步完善,薄膜铌酸锂光子芯片被用于集成单光子源、波导干涉器和光子探测器,以多模式耦合的独特优势实现更高精度、更快速度的量子态调控,为未来实用化量子计算提供了坚实基础。同时,基于该芯片构建的混合量子计算架构,更将为光量子计算的跨平台应用与多场景拓展提供核心技术支撑,加速推动光量子计算向实用化、规模化阶段迈进。

未来,依托中试线的可拓展优势,CHIPX将通过增补设备、拓展多材料体系、突破多材料异质集成技术,建设具备稳定量产能力的晶圆级光子芯片产线,打造全球最大规模的光子芯片产业基地。同时,研究院围绕芯、光、智、算等进行科技成果转化及孵投一体的创业孵化,为光子计算、量子信息、6G通信、激光雷达等产业提供核心保障,助力我国在新一轮科技革命中抢占战略制高点。

来源:新华社,爱科会易仅用于学术交流,若相关内容侵权,请联系删除。

入选国家工信部「首批重点培育中试平台」名单不到1个月,上海交大无锡光子芯片研究院(CHIPX)再次迎来重磅时刻——6月5日,首片6寸薄膜铌酸锂光子芯片晶圆在国内首个光子芯片中试线下线,同时实现了超低损耗、超高带宽的高性能薄膜铌酸锂调制器芯片的规模化量产,关键技术指标达到国际先进水平。

据悉,这一突破性成果标志着我国在高端光电子核心器件领域完成从「技术跟跑」到「产业领跑」的历史性跨越。研究院将依托中试平台,携手产业链合作伙伴推进规模化量产进程,构建「技术研发-工艺验证-规模量产」全链条能力,进一步增强自主可控的量子科技国际竞争力。

自主可控中试平台,实现晶圆级光子芯片集成工艺突破

光量子芯片是光量子计算的核心硬件载体,其产业化进程将推动我国在量子信息领域实现自主可控,更是抢占全球量子科技竞争制高点的战略支撑。此前,因共性关键工艺技术平台的缺失,我国光量子技术面临「实验室成果难以量产」的困境,是制约产业发展的「卡脖子」难题,而光子芯片中试线的启用成为破局关键。

作为无锡市滨湖区竞速量子科技赛道的「头号工程」,也是区域未来产业地标,上海交大无锡光子芯片研究院于2022年底破土动工,并率先启动国内首条光子芯片中试线建设。上海交大无锡光子芯片研究院于2022年12月启动国内首条光子芯片中试线建设,2024年9月,集光子芯片研发、设计、加工和应用于一体的光子芯片中试线正式启用。如今,首片晶圆成功下线,中试平台实现量产通线,彰显了项目建设的高效与成果。

作为一种高性能光电材料,薄膜铌酸锂具备超快电光效应、高带宽、低功耗等优势,在5G通信、量子计算等领域展现出巨大潜力。然而,由于薄膜铌酸锂材料脆性大,大尺寸薄膜铌酸锂晶圆的制备一直被行业视为挑战,尤其在量产化工艺中面临纳米级加工精度控制、薄膜沉积均匀性保证、刻蚀速率一致性调控等三大难题。

CHIPX工艺团队基于自主建设的国内首条光子芯片中试线,引进了110余台国际顶级CMOS工艺设备,覆盖了薄膜铌酸锂晶圆从光刻、薄膜沉积、刻蚀、湿法、切割、量测到封装的全闭环工艺。通过创新性开发芯片设计、工艺方案与设备系统的协同适配技术,成功打通了从光刻图形化、精密刻蚀、薄膜沉积到封装测试的全制程工艺,实现晶圆级光子芯片集成工艺突破。

性能指标国内领先,高性能薄膜铌酸锂调制器芯片实现规模化量产

凭借中试平台先进的纳米级加工设备和快速工艺迭代能力,工艺团队通过大量工艺验证与优化,以深紫外(DUV)光刻与薄膜刻蚀的组合工艺,系统性地解决了晶圆级光子芯片集成的关键技术瓶颈:在6寸铌酸锂晶圆上实现了110nm高精度波导刻蚀;通过步进式(i-line)光刻完成了高均一性、纳米级波导与复杂高性能电极结构的跨尺度集成,达到顶尖制程水平。

同时,工艺团队通过材料-器件协同设计创新,在兼顾高集成度的同时,实现了性能的跨越式突破,关键指标全面领先。

工艺纳入PDK体系,中试平台赋能产业生态

中试平台,一头连着创新,一头连着产业。在不断提升自身科技创新能力的同时,研究院还打造了开放共享的服务生态,赋能产业发展。

近期,研究院将发布PDK工艺设计包,本次高性能薄膜铌酸锂调制器芯片的核心工艺参数与器件模型已全面纳入、开放共享。该版本PDK不仅集成无源耦合器、分束器、波导阵列和有源热相移器、电光调制器等基础元件模型,同时涵盖多物理场协同仿真模块,构建起标准化光子芯片设计体系。

重构智算新范式,赋能国家战略需求

除了赋能产业发展,上海交大无锡光子芯片研究院此次双重成果突破更具里程碑意义,正加速推动芯片化光子集成趋势下的产业链重构进程。

在人工智能算力需求呈指数级增长的当下,传统电子器件面临功耗高、带宽受限两大核心瓶颈。高性能薄膜铌酸锂调制器凭借超低损耗、超高带宽、超快传输速率优势,能支撑云计算、超算中心和5G/6G基础设施的场景需求;基于该技术的光计算芯片,以「光传输+光计算」的融合方案,实现高并行、低延迟、低功耗的AI推理与训练计算架构,从底层破解AI大模型训练的算力困局,正成为AI算力新基建的核心支撑。

随着技术链逐步完善,薄膜铌酸锂光子芯片被用于集成单光子源、波导干涉器和光子探测器,以多模式耦合的独特优势实现更高精度、更快速度的量子态调控,为未来实用化量子计算提供了坚实基础。同时,基于该芯片构建的混合量子计算架构,更将为光量子计算的跨平台应用与多场景拓展提供核心技术支撑,加速推动光量子计算向实用化、规模化阶段迈进。

未来,依托中试线的可拓展优势,CHIPX将通过增补设备、拓展多材料体系、突破多材料异质集成技术,建设具备稳定量产能力的晶圆级光子芯片产线,打造全球最大规模的光子芯片产业基地。同时,研究院围绕芯、光、智、算等进行科技成果转化及孵投一体的创业孵化,为光子计算、量子信息、6G通信、激光雷达等产业提供核心保障,助力我国在新一轮科技革命中抢占战略制高点。

来源:新华社,爱科会易仅用于学术交流,若相关内容侵权,请联系删除。